Pos:

Home KnowledgeTechnologyDiamond heterojunction integration for thermal management of electronic device packagingWith the rapid development of AI technology and its enormous demand for computing power, 2.5D and 3D packaging technologies are receiving increasing attention. However, whether using silicon or glass adapters for 2.5D packaging, as well as 3D integration with multiple active chip stacks, the higher integration density and power density pose serious challenges to chip thermal management. The current cooling technology mainly relies on hot through-holes, uniform heat plates, forced air or liquid cooling, which result in larger external dimensions and significant energy consumption at the packaging or board level.

Diamond has extremely high thermal conductivity (1000-2200 W/(m.K)) and has broad prospects as a heat sink. At present, the artificial synthesis of diamond is limited to 5-inch wafers, resulting in its wafer level integration with semiconductor substrates being limited to smaller III-V group semiconductors and compound semiconductors (GaN, SiC); In addition, the growth temperature of artificial diamond exceeds 400 ℃, which can easily cause damage to the chip. Chip level integration can avoid the problems of small wafer size and high growth temperature. However, traditional chip bonding techniques, such as soldering and silver sintering, often introduce thicker solder layers, resulting in larger interfacial thermal resistance. There is an urgent need for a chip level diamond integration process with low temperature, low stress, and low interface thermal resistance.

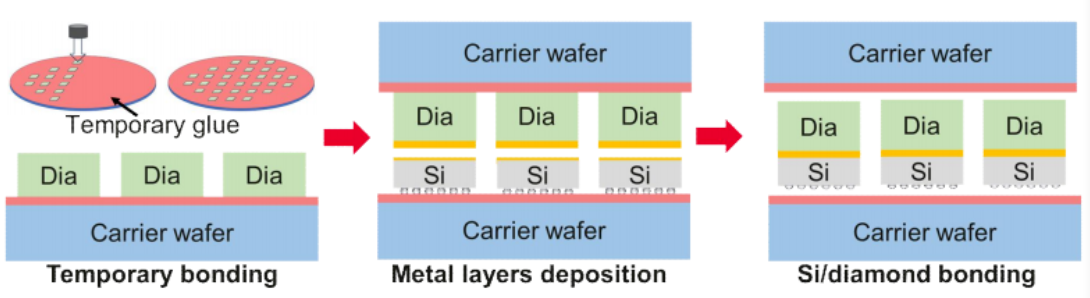

Recently, researchers have conducted research and verification on diamond heat dissipation technology using diamond low-temperature bonding and glass adapter plate 2.5D advanced packaging technology. The study utilized a nano metal intermediate layer to achieve low-temperature bonding between diamond and silicon thermal testing chips at 200 ℃, avoiding issues such as stress and micro protrusion damage caused by high-temperature processes. After testing the chip temperature, it was found to be between 1.5-2W/mm ² Under local power density, chips bonded with diamond can reduce the maximum temperature by nearly 20 ℃. This result demonstrates the excellent heat dissipation performance of diamond and the feasibility of applying diamond chip bonding technology. The advantage of chip level low-temperature bonding technology is that it does not require large-sized diamond wafers, while avoiding the high temperature and stress issues of diamond synthesis.

CSMH is committed to the production and research of diamond materials, with a mature product system, including diamond wafers, diamond heat sinks, diamond windows, diamond heterojunction integrated composite substrates, etc. Among them, the surface roughness of the diamond wafer Ra<1nm; The thermal conductivity of diamond heat sinks is1000-2200W/m.k, and the technical indicators have reached the world's leading level, which has assisted in the successful bonding process. Currently, diamond bonding materials include Si, InP, GaN, Ga2O3, GaAs, YAG, etc.

闽ICP备2021005558号-1

闽ICP备2021005558号-1Leave A Message